数字频率产生器

紧急复习紧急复习,在要做信号调制之前赶紧把上一次的数字频率生成器复习一下——已经什么都不知道了。

知识点需要:信号与系统里面的时域频域相位域,数字电路基础里面的DAC转换。

数字频率生成器

- 频率合成技术简介

所谓频率合成技术指的是将一个或者多个具有高稳定度和高精确度的

频率参考源,经过混频、倍频或者分频等处理,得到具有同样稳定度和精确度的所需要频率。

早在 20 世纪 30 年代,频率合成理论便已经形成,早期主要代表器件有可控晶体振荡器。这种频率合成器需要通过手动切换开关来输出频率,石英晶体的稳定度和准确度决定了输出频率的稳定度和精度。此后出现了釆用多个晶体振荡器产生所需频点的合成方法,与可控晶体振荡器相比,这种方法使用的晶体振荡器数量要少,成本要低。

随着电子技术的发展和通信领域对频率的精度和稳定度的要求的提高,出现了一种非相干频率合成技术。非相干频率合成指的是使用一个参考源产生与参考源具有相同的精确度和稳定度的频率的技术。主要有四种实现方法:

直接频率合成技术、间接频率合成技术、直接数字频率合成技术与混合式频率合成技术。

1) 直接频率合成技术

直接频率合成理论是指使用一个或多个参考频率源经过谐波发生器

产生各次谐波,然后经过分频、倍频、混频滤波等处理产生所需要的各个频点。这种方法产生的波形具有:相位噪声小、频率转换时间短、工作频段宽等优点。但是直接频率合成技术使用了大量的分频器、倍频器、混频器,电路比较复杂、成本较高、设备笨重,并且容易产生杂散,因此应用范围并不是很广。

2) 间接频率合成技术

间接频率合成又被称为锁相频率合成,根据反馈原理产生频率步进,采用锁相环技术,输出高稳定度频率。锁相环理论早在年就被提出来,但是直到世纪年代第一次被使用于电视接收机水平和垂直的同步扫描。锁相环就相当于一个窄带跟踪滤波器,对杂散有很好的抑止作用,但是频率转换时间比较长,且在单环的情况下频率分辨率也不是很好。

3) 直接数字频率合成技术

直接数字频率合成(Direct Digital Frequency Synthesis 即 DDFS,—般简称 DDS)是从相位概念出发直接合成所需要波形的一种新的全数字频率合成技术。1971 年,美国学者 J.Tierncy,C.M.Rader 和 B.Gold 提出一种采用数字技术从相位概念出发,直接合成所需波形的频率合成原理。限于当时的数字技术和器件工艺水平,直接数字频率合成的性能指标还无法与已有的频率合成技术相比,所以未能受到重视。近年来,数字技术和器件工艺水平不断的得到发展和提高,直接数字频率合成得到了快速发展,在频率转换、分辨率、相位连续性、正交输出以及集成化等方面的性能都超越了其他频率合成技术所能达到旳水平,为电子系统提供了高质量频率源。但是直接数字频率合成也存在一些难以克服的缺点,如:杂散指标差,输出频率较低。

4) 混合式频率合成技术

混合式频率合成是综合不同合成技术的优点,将多种频率合技术混合使用的方法,常用的混合方案有直接数字频率合成与锁相频率合成混合方案。直接数字频率合成的优点是频率分辨率高、频率转换快、相位连续,缺点是输出频率低,杂散比较大。锁相频率合成的优点是频率比较高,对信号杂散的分量能有效抑制,缺点是分辨率不够,频率转换慢。可见,二者具有互补性,将这两种技术结合起来,充分利用各自的优点,可以输出宽频带、高分辨率、低杂散和低相噪的频率。

2

综上所述,目前常使用的频率合成技术各有其特点,设计者需要根据设计需求综合考虑各种频率合成技术的优缺点,制定合理设计方案。在实际应用中,主要从以下几个技术指标考虑频率合成器的优缺点:

1) 输出频率范围:频率范围即频率合成器的最低输出频率和最高输出频率之间的间隔。

2) 频率分辨率:频率分辨率又称频率步进,指的是两个相邻的输出频点之间的最小间隔。

3) 频率稳定度:频率稳定度是指在一定时间内,输出频率偏离标准频率的大小,分为长期稳定度和短期稳定。长期稳定度是指由于元件老化引起的元件参数变化和工作环境的变化引起的频率漂移。短期稳定度是输出频率在秒或者毫秒单位内的频率起伏,影响短期频率稳定度的主要原因是各种随机噪声。

4) 杂散指标:杂散指标是表示输出的频率中包含不需要的信号成分它表征频率源的输出谱的纯度。杂散的产生主要有三个因素:①外部的福射干扰;②系统内部频率成分的福射;③在频率合成过程中产生。

5) 相位噪声:相位噪声是频率稳定度的频域表示,表现为在主频两边的连续噪声。

6) 频率转换速度:频率转换速度是从个工作频率转换到另一个工作频率所需要的快慢的表征。

——————————————————废话结束————————————————————————————————————

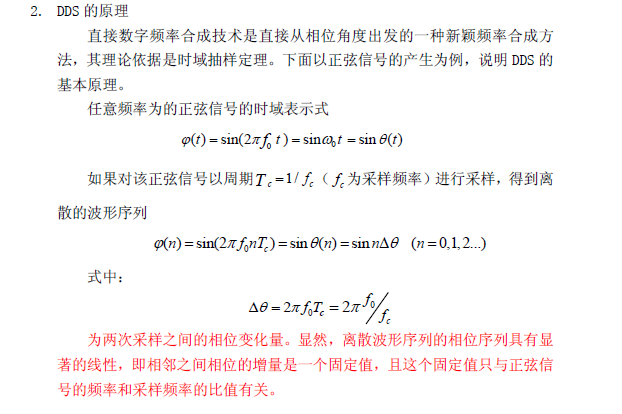

- 原理分析来自保骏的实验开发指导书,可能摘自《通信原理》

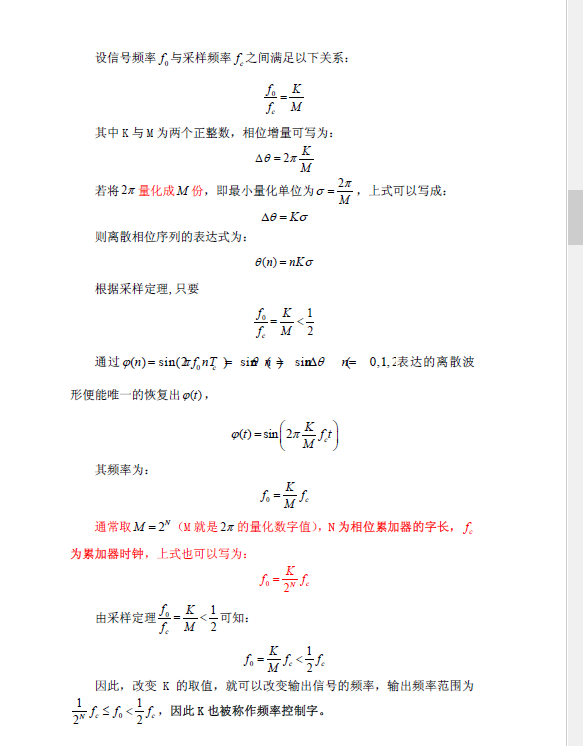

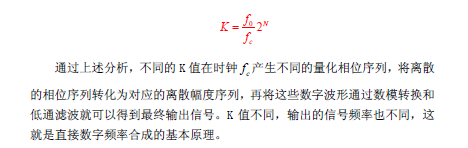

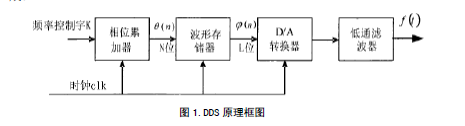

从以上原理可见, 通过控制K 和采样频率,可以通过相位累加器获得想要得到频率波形的相位信息。

之后我们通过相位信息映射内存地址,从某个存储了幅值信息的rom中获取正弦波的幅值输出(查找表方法),通过DAC转换成模拟波形。

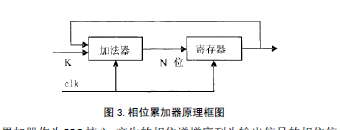

相位累加器

使用一个加法器,每次对频率控制字K进行累加,K越大,每次累加的步进越大。

对于特定的频率生成器K,其对应的生成频率为 Kfc/2^N;K=1时,输出最小波形频率nabla=fc/2^N。

相位累加器采用二进制进行计算方便、快速,但不能保证输出频率为整数,会产生一定的误差。比如,时钟频率为10MHz,相位累加器的位数为32, 则最小输出频率分辨率为:

0.0233Hz=10^7/2^32;

可以通过增加累加器位数(使分辨率更小),调整时钟频率(使输出频率为负数防止舍去)来减小误差。

使用成本更高的十进制累加器可以完全解决问题。

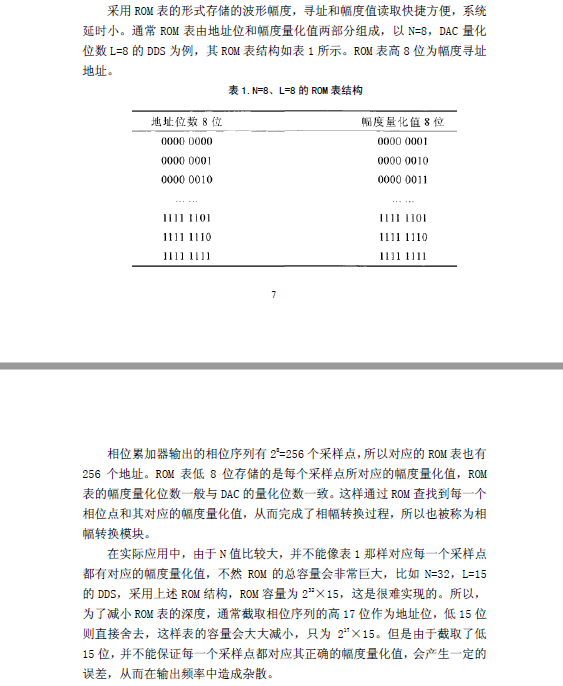

波形存储器

波形存储器用于存储波形一个周期的幅值信息。可以使用rom,也可以使用不同的存储器。

原生杂散和后期处理杂散都会suffer from 这个截取。

在指导书的叙述中,不明白为什么当DAC量化位数为15,ROM地址线位数为32时候,ROM容量为2^32×15——每个rom地址都有15个DAC输出量化结果?

等待补充回答遗留问题

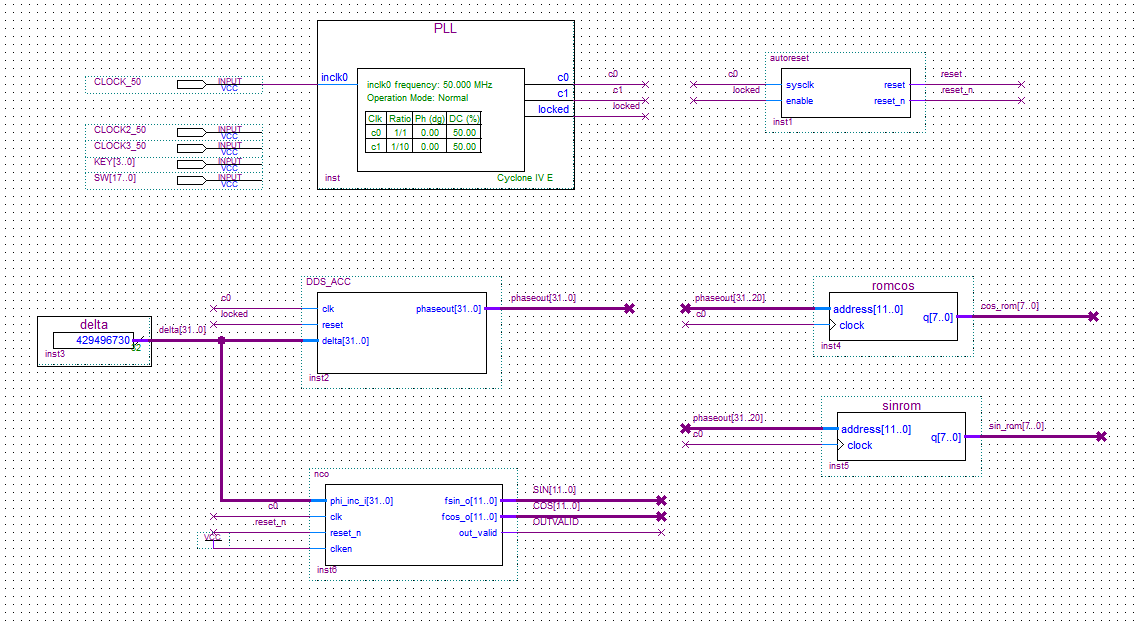

FPGA顶层设计图:

其中一边使用NCO内置模块直接生成波形(原理未知),一边使用上文介绍原理从内存中拉取幅值信息进行DAC转换输出。

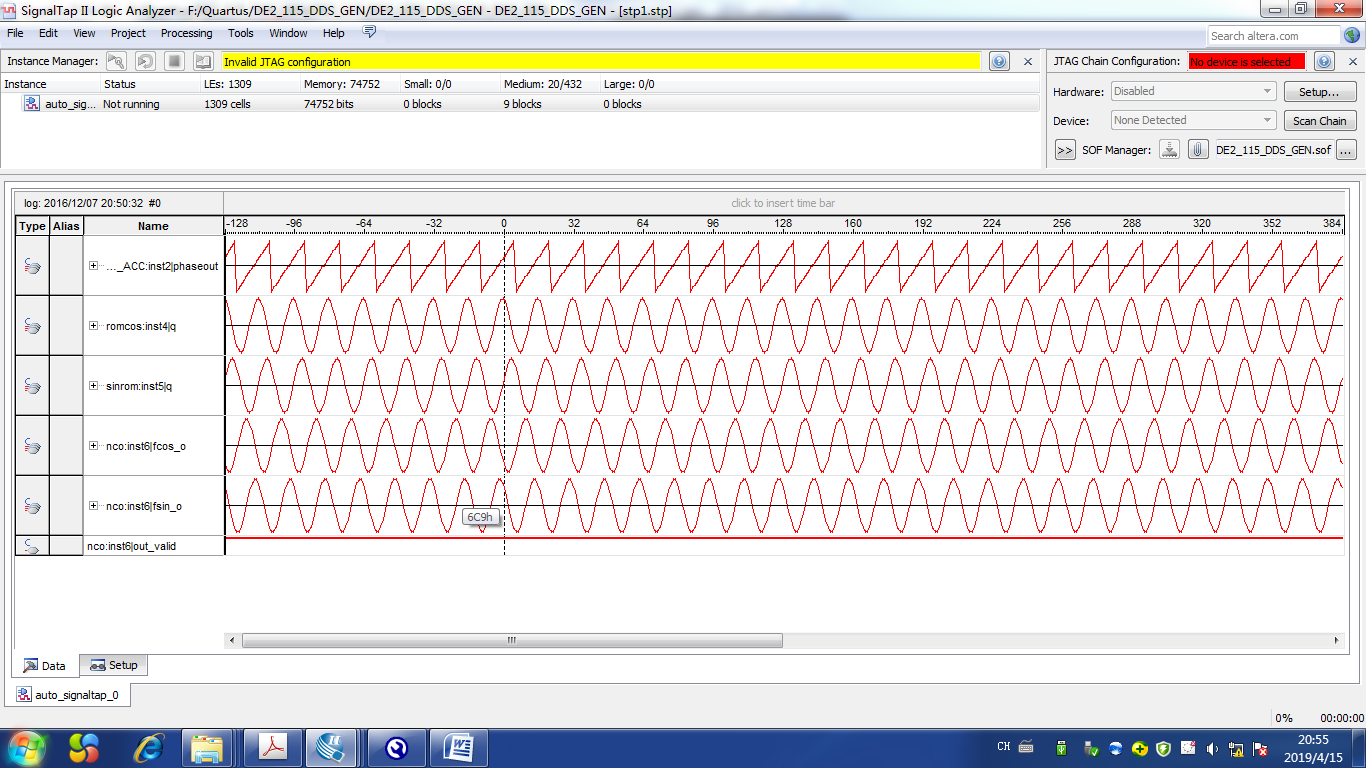

波形图